TRS 80 Japan Modell aufbohren

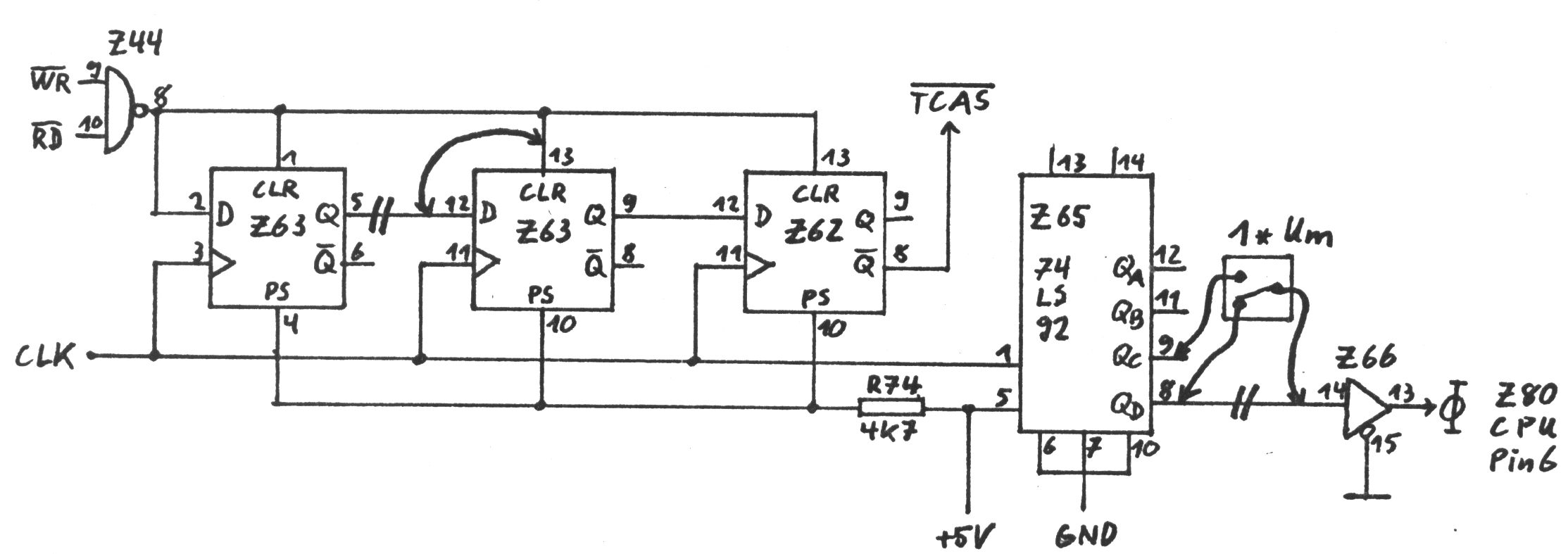

auf1,77/3,55 MHz Takt-Umschaltung

CP/M-Fähigkeit

256K gebanktes RAM

H. Bernhardt

Aufgrund eines mir zunächst üppig erschienenen, sich aber nachträglich als keinesfalls dem Aufwand adäquat erwiesenen Honorars ließ ich mich breitschlagen, in einem vermeintlichen TRS 80 Modell 1 einen 256K-Banker, einen CP/M-Banker und eine einfache Taktumschaltung einzubauen. Bei Übernahme des Gerätes stellte sich aber heraus daß es sich um ein Japan-Modell (* siehe Ende des Artikels) handelt, bei dem alle meine Unterlagen zum TRS 80 unbrauchbar sind. Es galt also zunächst dessen Schaltung zu analysieren, um dann die nötigen Änderungen für die Erweiterungen vorzunehmen und zu sehen, an welchen Punkten die benötigten Signale abzugreifen sind. Solches hatte ich vor Jahren beim Komtek 1 schon mal durchgeführt, so daß mir der Mut nicht ganz verlorengegangen war.

|

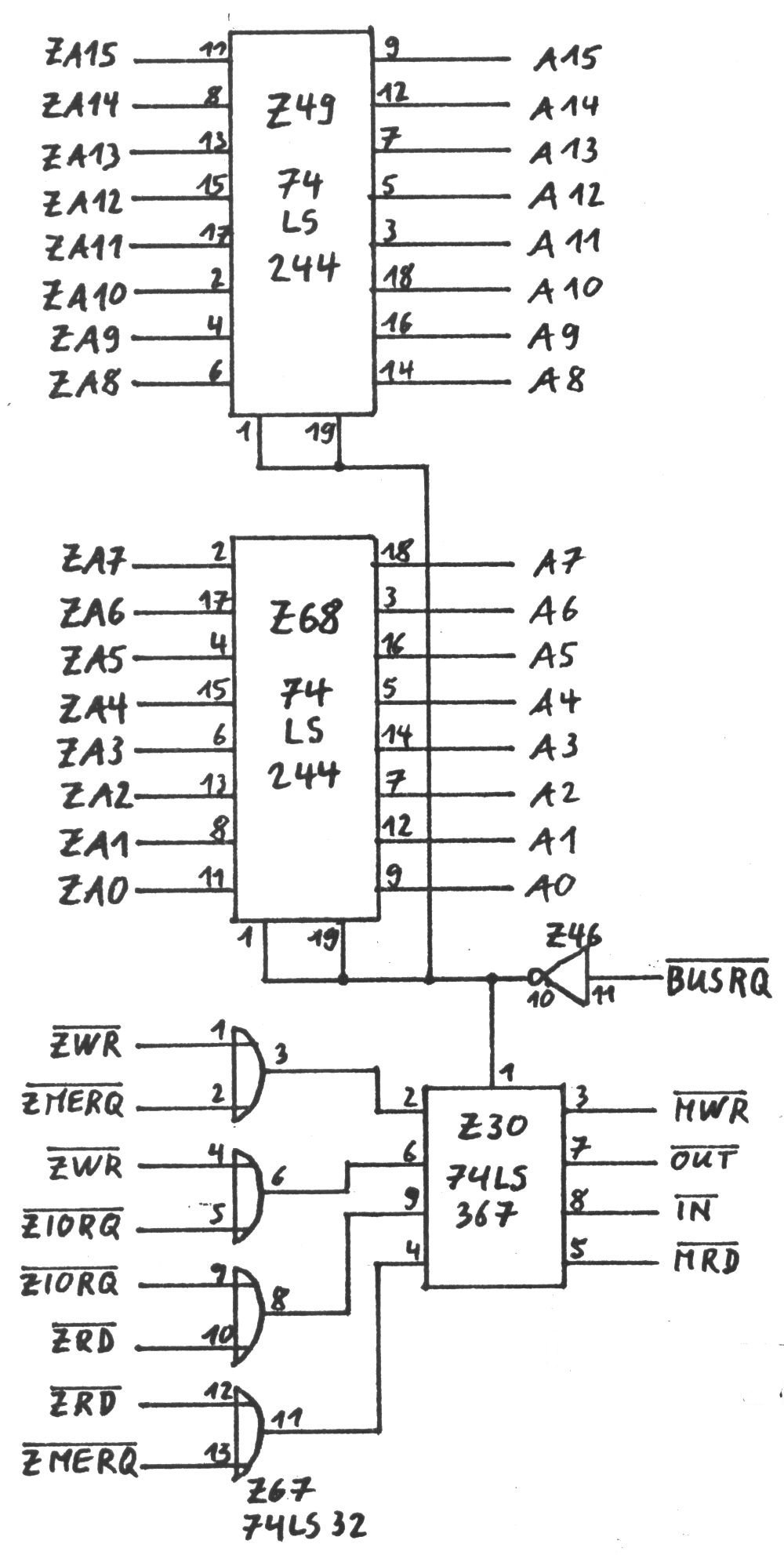

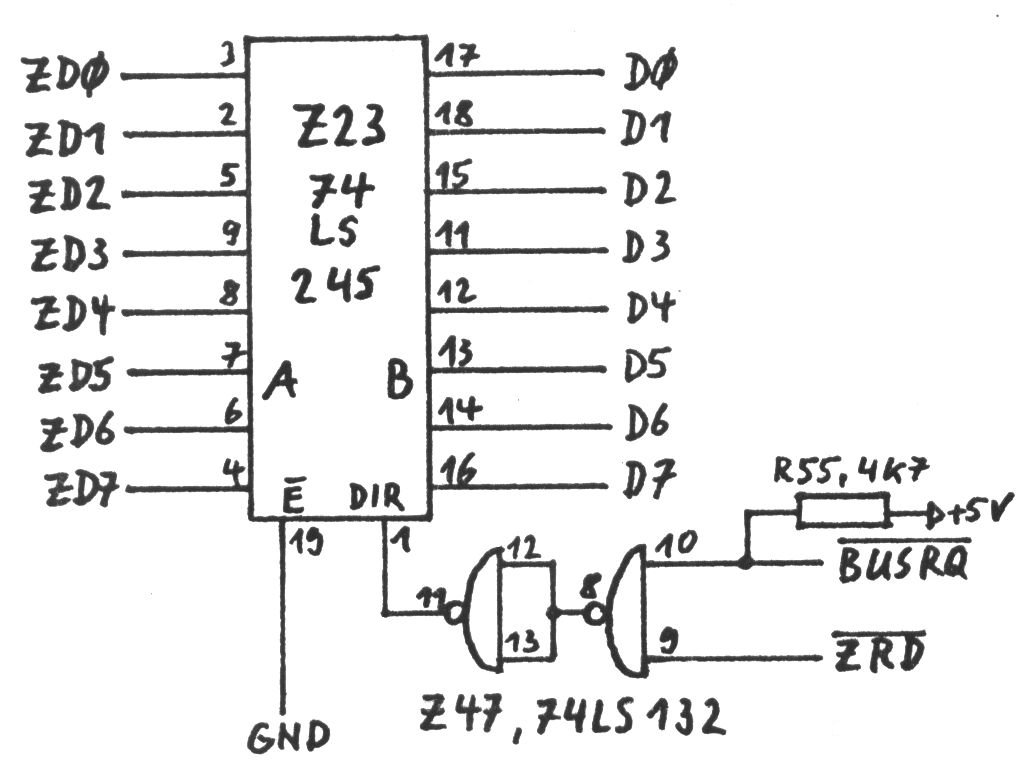

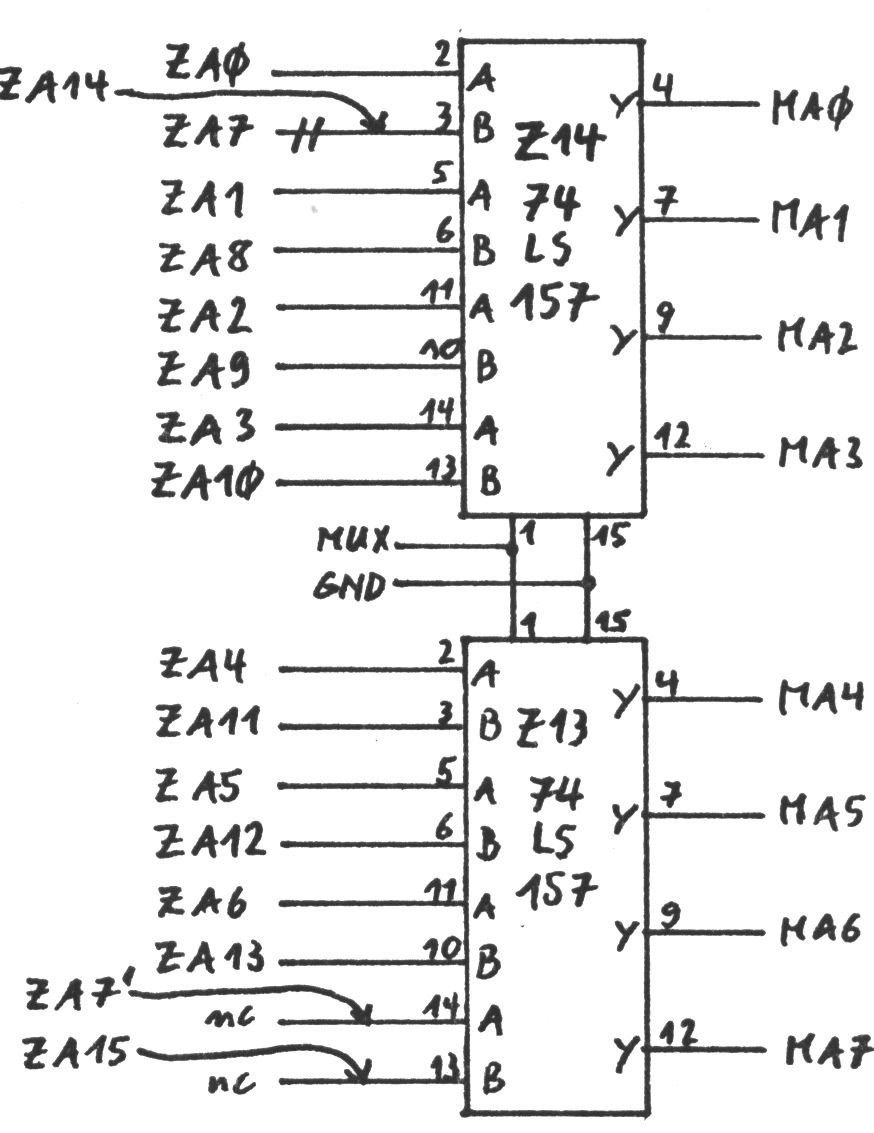

Abb.1: links: Treiber für Adressen und Daten des Z80 (die mit Z.. bezeichnexen Signale sind die des Z80) sowie Erzeugen der Signale MWR*, MRD*, 0UT* und IN* rechts: Adreßmultiplexer für die RAMs (eingezeichnet sind die Änderungen für 4164-RAMs mit 7- oder 8-Bit-Refresh. Für 8-Bit-Refresh-RAMs muß ZA7' von einem Generator für 8-Bit-Refresh-Adressen kommen) |

Eventuell besitzt hier im Club noch irgendjemand diese Variante des TRS 80 (vielleicht, ohne es selbst zu wissen, denn äußerlich sehen Original und Fälschung gleich aus), dem die von mir extrahierten Informationen etwas nützen. Deshalb will ich es riskieren, einige Seiten des kostbaren Platzes in diemem Info für diesen Zweck zu verbrauchen. Den 256K-Banker habe ich vor längerer Zeit schon einmal im Club 80 Info beschrieben, so daß hier nur noch dessen Einbau und Anschluß am CPU-Board breitgetreten werden soll.

Den CP/M-Banker (für den es ein angepaßtes CP/M 3,O BIOS gibt, zu dem auch die Source-Codes vorliegen) habe ich vor noch längerer Zeit zusammen mit Christof Ueberschaar entwickelt und im Info des mittlerweile eingegangenen Bremerhavener TRS 8O/GENIE-Clubs veröffentlicht. Um die zahlreichen Mitglieder des Club 80, die dort auch mal Mitlied waren, nicht noch einmal damit zu langweilen, soll nur die Schaltung dieses CP/M-Bankers und eine Skizze mit den Anschlußpunkten auf dem Platinchen vorgestellt werden, wer darüber hinaus Interesse an dem Artikel hat, kann sich mit 1,90 DM Rückporto im Brief bei mir melden.

Der CP/M-Banker setzt voraus, daß im Grundgerät 64K oder 256K RAM vorhanden sind. Durch Ausgabe des Bytes 00H an den Port 50H wird der ROM-Bereich abgeschaltet und im Bereich 0000H-37DFH wird RAM verfügbar gemacht. Diese Einstellung läßt sich durch Software nicht wieder rückgängig machen. Nur ein RESET stellt wieder die urspünglichen ROMs bereit. Durch ein kleines Maschinenprogramm kann der ROM-Inhalt nach oben kopiert werden dann der Umschaltbefehl ausgeführt und schließlich der ROM-Inhalt an seine ursprüngliche Adresse zurückgeschoben werden. Damit ist das Level 2 ROM weich geworden und kann beliebig gepatcht werden.

Wenn an den Port 50H der Wert 40H (D6=1) ausgegeben wird, ist anschließend auch noch der memory mapped I/0-Bereich 37E0H-3FFFH nach F7E0H-FFFFH verlegt worden, so daß ein fast 64K großer RAM-Bereich ab 0000H vorliegt, womit CP/M leben kann.

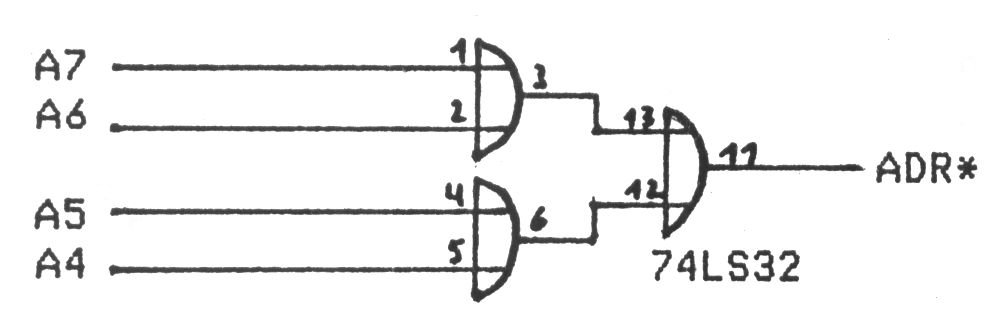

Es sei noch gesagt, daß die Verwendung des Ports 50H (redundant decodiert auf 50H-5FH) bei gleichzeitig vorhandener HRG1B wegen deren Verschleiß an Portadressen (00H-7FH) eine feinere Decodierung der HRG1B erfordert. Prinzipiell genügt es, anstelle von A7 (an die HRG1B) ein aus A7 und A6 OR-verknüpftes Signal an die Karte zu führen, damit reduziert sich deren Portadreßhunger auf den Bereich 00H-3FH. Da dann aber ohnehin ein zusätzliches IC 74LS32 nötig ist, läßt sich die HRG1B auch noch auf die Portadressen 00H-0FH beschränken.

Abb.0: Dieses Signal reduziert den Portadreßhunger der HRG1B auf 00H-0FH wenn es anstelle von A7 die Port Freigabe steuert

Aber zurück zum Anschluß der Banker an das CPU-Board des Japan-Modells. Zunächst sollen die Änderungen besprochen werden, die den Einsatz von 64K bzw. 256K RAM Chips auf dem CPU-Board ermöglichen.

Auswechseln der 4116-RAMs

Dafür müssen die unsinnigerweise eingelöteten 4116-RAMs entfernt werden. Es werden alle Pins aller RAMs (Z15-Z22) möglichst hoch abgekniffen und die verbleibenden Stümpfe der Pins einzeln ausgelötet und schließlich die Lötlöcher mit einer Entlötpumpe freigemacht.

Vor dem Einlöten der DIL16-Fassungen für die neuen RAMs sind noch ein paar Änderungen nötig, um die +12V-Versorgung von den Pins 8 der RAMs und die -5V-Versorgung von den Pins 1 der RAMs zu entfernen und die +5V-Versorgung von den Pins 9 zu den Pins 8 der RAMs zu verlegen, und um an die Pins 9 ein neu zu erzeugendes gemultiplextes Signal MA7 (und bei 256K-Chips an die Pins 1 ein MA8) zu führen. Dafür sind folgende Arbeiten durchzuführen:

- Alle Kondensatoren (100nF) oberhalb und unterhalb der RAMs, die mit einem Beinchen Kontakt mit den Pins 1 oder 9 der RAMs haben, werden ausgelötet. Die bestückungsseitige, breite, die Pins 1 der RAMs verbindende Leiterbahn wird auf Höhe der 33-Ohm-Widerstände (R101) durchtrennt (-5V an den Pins 1 der RAMs).

- Die lötseitige, breite, um RAM Z15 und die 33-Ohm-Widerstände herum zu Pin 16 von Z14, 74LS157 führende Leiterbahn wird auf Höhe der 33-Ohm Widerstände (R101) durchtrennt (+5V an den Pins 9 der RAMs).

- Die vom Kondensator C15 auf der Lötseite zu Pin 8 von Z19 (RAM) verlaufende breite Leiterbahn wird neben C15 durchtrennt (+12V an den Pins 8 der RAMs).

- Eventuell müssen lötseitig noch einige zusätzliche Kondensatoren von 100nF über die Pins 8 und 16 der RAMs gelegt werden. Optimal ist ein 100nF- Kondensator je RAM. Diese Kondensatoren sollten nach dem Einlöten der DIL16- Sockel für die neuen 4164- bzw. 41256-RAMs lötseitig an die Pins 8 und 16 der Sockel gelötet werden. Es ist dafür zu sorgen, daß keine Kontakte zu anderen Pins entstehen (Isolierhülsen auf die Beinchen der Kondensatoren).

- Für den Einsatz von 4164-RAMs mit 7-Bit-Refresh reicht es, wenn A15 von Z48 Z80-CPU, Pin 5 an Pin 13 von Z13, 74L5157 und A14 von Z48, Z80-CPU, Pin 4 mit den untereinander verbundenen Pins 9 der RAMs verdrahtet wird.

- Für den Einsatz von 4164-RAMs mit 8-Bit-Refresh oder 41256-RAMs (mit grundsätzlich 8-Bit-Refresh) muß A7 von Pin 3 von Z14, 74LS157 abgetrennt werden. Die lötseitige Leiterbahn zu Pin 3 von Z14 wird direkt neben dem Pin 3 durchtrennt.

- An diesen Pin 3 wird dann A14 von Z48, Z80-CPU, Pin 4 verdrahtet. A15 von Z48, Z80-CPU, Pin 5 wird mit Pin 13 von Z13, 74LS157 und Pin 12 von Z13 wird mit den Pins 9 der RAMs verdrahtet. A7' von einem 8-Bit-Refresh-Generator (z.B. auf dem 256K-Banker) wird an Pin 14 von Z13, 74LS157 gelegt.

- Im Expansion-Interface des Japan-Modells (schwarzes Blechgehäuse) werden alle

RAMs 4116 aus den Fassungen gezogen und verworfen.

Neben den RAMs befinden sich 2 Stück 74LS244-Treiber. Bei beiden ICs wird die bestückungsseitig von den Pins 1 wegführende Leiterbahn direkt neben den Pins 1 durchtrennt. - Auf der Lötseite wird die die Pins 19 der 74LS244-ICs verbindende Leiterbahn neben der Durchkontaktierung beim 74LS32-IC durchtrennt. Bei beiden 74LS244- ICs wird eine Verbindung zwischen den Pins 1 und 19 hergestellt. Auf der Bestückungsseite wird an einem der 74LS244-ICs ein Widerstand von 2k2 von Pin 1 nach Pin 20 gelegt.

Taktumschaltung

Nach dieser Änderung sollte bei Verwendung von 4164-RAMs mit 7Bit-Refresh der Computer normal mit 48K RAM arbeiten. Da die langsamen RAMs im Expansion- Interface nun nicht mehr benutzt werden, läßt sich eine Speed-Umschaltung zwischen 1,77MHz und 3,55MHz einbauen. Die hier mit einem einfachen Umschalter realisierte Variante schaltet einen der beiden Takte zur CPU durch. Das

Umschalten ist also nicht während des Betriebs möglich (sollte es zumindest nicht, hier hat es in den meisten Fällen ohne Systemabsturz geklappt). Für diese Umschaltung sind folgende Operationen durchzuführen:

Abb.2: Änderungen für die Umschaltung des Systemtaktes

zwischen 1,77 und 3,55 MHz

Abb.2: Änderungen für die Umschaltung des Systemtaktes

zwischen 1,77 und 3,55 MHzAuf der Bestückungsseite

- wird die Leiterbahn, die zwischen Pins 13 und 14 von Z65, 74LS92 herauskommt

und zwischen Pins 2 und 3 von Z66, 74LS367 verschwindet, durchtrennt.

Die Pins 12 und 13 von Z63, 74LS74 werden miteinander verbunden.

Die Pins 8 und 9 von Z65, 74LS92 werden an die Außenkontakte eines Umschalters gelötet. Der Mittelkontakt des Umschalters wird mit Pin 14 von Z66, 74LS367 verbunden (möglichst kurze Leitungen).

- wird die Verbindung von Pin 12 von Z63, 74LS74 zur Durchkontaktierung unter dem IC durchtrennt.

CP/M-Banker einbauen

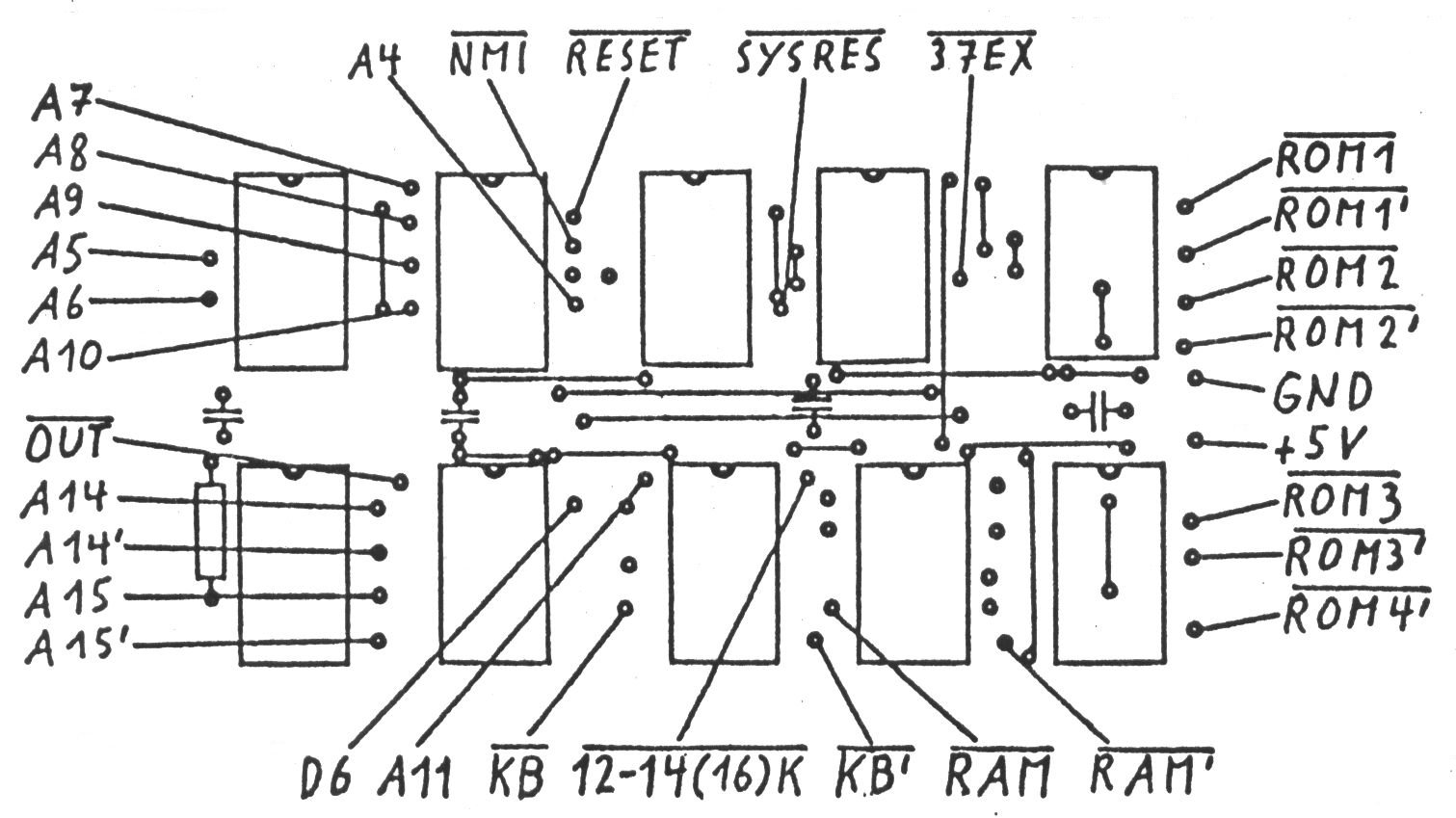

Abb.3: Änderung an der Adreßdecodierung des CPU-Boards und Anschluß des CP/M-Bankers

für den Anschluß des CP/M-Bankers sind die in Abb.3 dargestellten Änderungen in der Adreßdecodierung der unteren 16K auf dem CPU-Board vorzunehmen. Im einzelnen bedeutet dies folgende Arbeiten:

Bestückungsseite:- Die Leiterbahn, die zwischen den Pins 2 und 3 von Z65, 74LS92 herauskommt und zwischen den Pins 11 und 12 von Z64, 74LS32 verschwindet, wird durchtrennt.

- Der Pin 3 von 266, 74LS367 wird mit Pin 13 von Z64, 74LS32 verbunden.

- Der Pin 6 von Z64, 74LS32 wird mit Pin 12 von Z44, 74LS00 verbunden. Die von Pin 12 von Z49, 74LS244 zur ca. 2 cm entfernten Durchkontaktierung

- führende Leiterbahn wird durchtrennt (A14).

- Die daneben verlaufende (zwischen den Pins 11 und 12 von Z49, 74LS244 herauskommende) Leiterbahn wird durchtrennt (A15).

- Die an Pin 10 von Z61, 74LS139 führende Leiterbahn wird neben dem Pin durchtrennt.

- Die Leiterbahn von Pin 11 von Z64, 74LS32 zur Durchkontaktierung bei Pin 8 von Z64, 74LS32 wird durchtrennt.

- Die Leiterbahn von Pin 13 von Z44, 74LS00 zur Durchkontaktierung wird durchtrennt.

- Die Verbindung zwischen den Pins 2 und 6 von Z64, 74LS32 wird durchtrennt.

- Die Leiterbahn von der Durchkontaktierung auf Höhe der Pins 5 und 10 von Z64, 74LS32 zur Durchkontaktierung auf Höhe der Pins 3,4,11 und 12 von Z44, 74LS00

- wird durchtrennt.

- Das IC Z10, 74LS32 wird nicht bestückt und der Jumper J5 bleibt offen. Die Jumper J1, J2, J3 und J4 werden gelegt.

- Die Anschlüsse SYSRES*, ROM3*, ROM4*, ROM3'*, ROM4'* sowie 37EX* bleiben unberücksichtigt.

Der CP/M-Banker wird gemäß folgender Tabelle mit dem CPU-Board verbunden:

Signale auf dem Anschluß auf dem

CP/M-Banker CPU-Board

------------------------------------

A4 Z68 74LS244 Pin5

A5 " " 16

A6 " " 3

A7 " " 18

A8 Z49 74LS244 Pin14

A9 " " 16

A10 " " 18

A11 " " 3

A14 " " 12

A15 " " 9

------------------------------------

12-14(16)K* Z61 74LS139 Pin15

0UT* Z30 74LS377 Pin7

RESET* Z46 74LL04 Pin12

NMI* Z45 74LS02 Pin10

ROM1* Z60 74LS11 Pin8

ROM2* Z61 74L5139 Pin6

RAM* Z64 74LS32 Pin11

KB* Z61 74LS139 Pin10

------------------------------------

ROM3'* Z42 ROM A Pin20 diese Pins werden aus

R0M2'* Z43 ROM B Pin20 der Fassung gebogen

RAM'* Z49 74LS367 Pin15

KB'* Keyboard-Stecker Pin10

A14'* an die Durchkontaktierung, deren Verbindung zu Pin 12

von Z49, 74LS244 durchtrennt wurde

A15'* an die Durchkontaktierung direkt daneben

Abb.5: Anschlüsse an das CPU-Board

256K-Banker einbauen

Um den Anschluß des 256K-Banker vorzubereiten, wird auf Z14, 74LS157 noch ein weiteres IC 74L5157 mit den Pins 1, 8, 15 und 16 huckepack-gelötet; alle anderen Pins dieses ICs werden waagerecht abgebogen. An dieses IC Z14' werden die Signale A7', A15', A16 und A17 des 256K-Bankers angeschlossen

Signal des Bankers Pin von Z14'

-----------------------------------

A7' Pin14

A15' " 13

A16 " 11

A17 " 10

-----------------------------------

Die Pins 9 der RAMs werden mit Pin 12 von Z14' und die Pins 1 der RAMs mit Pin 9 von Z14' verbunden. Die eventuell beim Umbau auf 64K RAM (event. mit CP/M-Banker) hergestellte Verbindung zwischen Pin12 von Z13 und den Pins 9 der RAMs wird wieder entfernt. Das anstelle der durchtrennten Leiterbahn (A7 der Z80-CPU) an Pin 3 von Z14 geführte Signal A14 (Pin 4 der Z80-CPU) bleibt angeschlossen.

Die Eingangssignale für den 256K-Banker werden an folgenden Punkten auf dem CPU-Board entnommen und an die entsprechend bezeichneten Punkte des 256K-Bankers geführt (freie Verdrahtung).

Signal CPU-Board 256K-Banker IC Typ Pin Anschlußpunkt -------------------------------------- D0 Z23 245 17 g D1 " " 18 f D2 " " 15 e -------------------------------------- A0 Z68 244 9 8 A1 " " 12 9 A2 " " 7 1 A3 " " 14 2 A4 " " 5 10 A5 " " 16 4 und 5 A6 " " 3 6 und m A7 " " 18 7 und n A15 Z49 244 9 h -------------------------------------- SYSRE5* (siehe unten) a 0UT* Z30 377 7 l RFSH* Z49 Z80-CPU 28 o --------------------------------------

Bei "nur" 256K RAM werden die Eingangssignale D3 und D4 sowie CASEN*

und die Ausgangssignale CASEN1* bis CASEN4* nicht angeschlossen.

Das Signal SYSRES* wird auf dem CP/M-Banker aus RESET* und NMI* erzeugt und

kann von dort bezogen werden. Wenn der CP/M-Banker nicht eingebaut wird, muß

RESET* (von Z46, 74LS04, Pin 12) oder NMI* (von Z45 74LS02, Pin 10) stattdessen

verwendet werden.

Bei den spartanischen Platzverhältnissen im TRS 80 Modell 1 muß beim Einbau von Erweiterungen von vornherein geplant werden, wo die zusätzlichen Platinchen in der Schachtel Platz finden. Das CPU-Board liegt mit der Bestückungsseite nach unten im Gehäuse. Erweiterungen, die darunter liegen sollen, müssen also von der Bestückungsseite her angeschlossen werden. Platz ist unter dem CPU-Board nur in der hinteren Hälfte des Gehäuses vorhanden. Die Anschlußdrähte sollten also gleich so lang gewählt werden, daß diese Einbaulage möglich ist. Allerdings ist in digitalen Schaltungen prinzipiell das Einhalten kurzer Leitungslängen anzustreben. Man sollte also auch nicht zu großzügig mit der zu verwendenden isolierten Litze umgehen.

Obwohl so mancher rechtschaffener Standard-Z80 die 3,55MHz besser verträgt als mancher A-Typ, sollten doch die paar Mark und fünfzig für einen auf 4MHz ausgelegten Z80A investiert werden. Dagegen ist die Investition für die neuen RAM-Chips bei den heutigen Preisen durchaus die Überlegung wert, ob man das dem alten Möbel noch angedeihen lassen will.

Außerdem ist (auch wenn für einen potentiellen Nachbauer der Aufwand für die Analyse des Japan-Modells entfällt) der Arbeitsaufwand und die Wahrscheinlichkeit, einen Fehler zu machen, recht hoch. Der eigene Performance-Ehrgeiz sollte also ruhig überschlagen werden. Auch die CP/M-Fähigkeit ist bei einem nach wie vor auf 64x16 Zeichen beschränten Bildschirm begrenzt tauglich und Tasten für deutsche Umlaute hatte ein TRS 80 Modell 1 noch nie.

Anmerkung Juni 2015:

Damals gab es noch kein Internet und ich konnte mir keine Abbildung des TRS80

Japan Modells ansehen. Anhand des Unterschiedes des CPU-Boards zu mir zugänglich

gewesenen TRS80 Geräten meinte ich, ein Japan-Modell vor mir zu haben. Das war

aber etwas anderes.